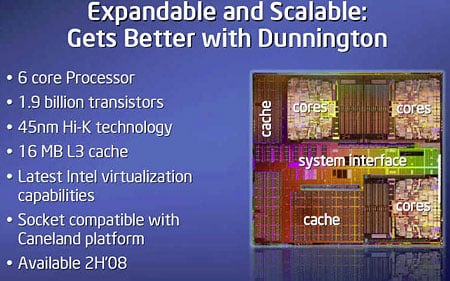

Pat dove in quickly with what was probably Intel's most ambitious design effort yet, that will bear fruit some time in 2H '08, the new six-core infused Dunnington server/workstation processor.

Intel Dunnington CPU architecture

Six cores and 16MB L3 cache

Some of the more interesting take-aways with Dunnignton were that Intel has re-tooled a shared L2/L3 cache architecture and that Dunnington will in fact be socket compatible with their current Caneland platform. However, we would expect that actual drop-in compatibility is guaranteed only by system board manufacturers with capable power circuits and up to date BIOS microcodes. Pat also stressed that Dunnington, though comprised of some 1.9 billion transistors and 16MB of L3 cache, will adhere to Intel's current power efficiency characteristics of their advanced 45nm Hi-K processing technology. Several systems were referenced in a recent third-party SPECpower Energy Efficiency test, showing Intel's current leadership with the Xeon 5400 and 5300 series of products in the top ten slots currently in the industry.

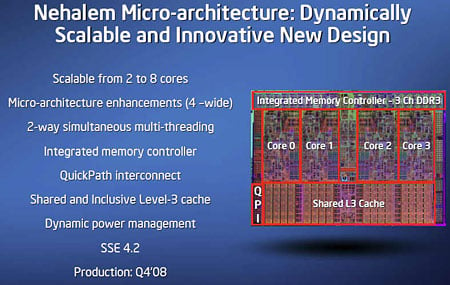

Next, Gelsinger stepped up with Intel's mainstream big gun, the company's forthcoming Nehalem quad core processor. Nehalem is slated to be Intel's first mainstream desktop product with a direct-attached serial interface, dubbed QPI or QuickPath Interconnect, a monumental upgrade over their now seriously aging Front Side Bus architecture.

The Nehalem core CPU architecture

4 Cores, QuickPath Interconnect, integrated memory controller, eight threads

Easily one the most interesting and talked-about aspects of Nehalem, Intel's new QuickPath Interconnect will provide for high speed, low latency transactions coming on and going off chip. Previously, one way Intel was able to mitigate FSB latency and bus turn-around times, was with larger amounts of L2 cache that provided more on-chip memory resources and thus required fewer requests over the FSB and out to system memory. Nehalem however, will have only 256K of L2 cache per core and a 8MB of L3 cache per chip. Comparatively, AMD's future 45nm quad core Phenoms will have 512K of L2 cache per core and 6MB of L3 total. Obviously Intel knows their architecture best but clearly this cache architecture seems a bit spartan versus previous Intel architectures, though admittedly exorbitant amounts of on-chip cache should no longer be a requirement with the new QPI interface at Nehalem's disposal.

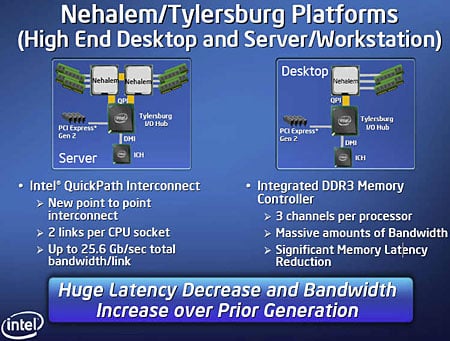

Intel Tylersburg Platform with DDR3, QPI and Gen2 PCI Express

And of course let's not forget the now fully integrated three channel DDR3 memory controller that Nehalem will bring with it to the platform. With support for three DIMMs per channel, total system memory densities can scale to a whopping 18GB of RAM total. That ought to run Vista well enough we think. The real key here for performance aficionados and high-end workstation types however, will be the lower overall latency and higher available bandwidth (up to ~ 32GB/sec) with Nehalem's on-board memory controller. We're anxious to see this in action. Coupled with QPI, the chip should have ultra-low latency characteristics in many areas. In addition, Nehalem's architecture will provide for two, four and octal-core designs with these easily configurable serial links.

In closing on the Nehalem processor itself, Gelsinger noted that Nehalem will also offer significantly improved multi-threaded performance, with up to a 33% improvement in available simultaneous micro-ops, more efficient cache management and higher performance branch prediction, with an added second level branch predictor. Finally Gelsinger noted that though Nehalem won't have any features on board formally known as Hyperthreading, he did note that per-core multithreaded performance will in fact be significantly improved over their Pentium 4 Netburst architecture.

Intel noted that they expect Nehalem to ship sometime in Q4 '08 and their next generation Westmere and Sandy Bridge processors, based on 32nm die geometries, will be introduced in 2009 - 2010. In addition, Intel will bring out a new instruction set with Sandy Bridge, branded "AVX" for Advanced Vector Extensions, that is aimed at beefing up SSE with 256-bit vector extensions for higher performance floating point calculations. Next, Pat segued into new frontiers in what Intel calls "visual computing" or what the rest of the world knows now as 3D graphics.

ntel's Gelsinger brought their quick, efficient press conference to a close with a shot across the bow of NVIDIA and AMD-ATI, giving us a view into their forward-looking Larrabee visual computing architecture. Only described by Gelsinger as a "many core" design, Larrabee is expected to take advantage of a scalable array of IA cores and a new cache architecture, along with a new vector instruction set; complimentary to, or a super-set perhaps of AVX.

Larrabee will also have a custom-designed vector processing unit and a highly programmable architecture that will make it useful for traditional graphics workloads HD Digital Video processing and 3D effects like global illumination. And although Intel will be fostering other methods of 3D rendering like ray-tracing, the chip will be compatible with DirectX and OpenGL and is expected to offer "competitive" performance to incumbent GPU architectures from NVIDIA and AMD-ATI. Gelsinger was quick to point out that the ISV and developers he has spoken to about Larrabee are extremely excited about its prospects, more so than any other architecture he's been involved with recently at Intel. We're told that Intel will demo Larrabee later this year with a launch sometime in 2009 or beyond.

No comments:

Post a Comment